## **Shift Registers Circuits**

**Objective:** Using D flipflops construct various types of shift registers and study Psuedo random number generation using Shift Registers.

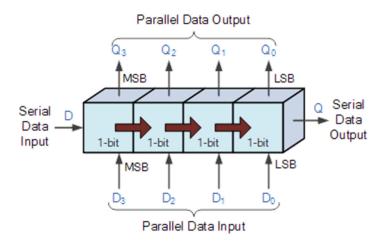

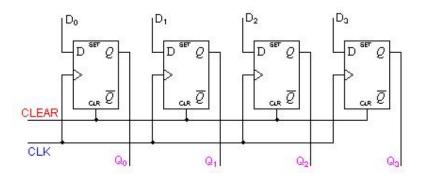

**Background**: Shift registers are vital in applications involving storage and transfer of data in a digital system. Shift Register is made with connecting D(Data) Flip Flops. Data is binary number either 1 or 0. Four different types of Shift Registers are possible as shown in the figure.

Fig. Four types of Shift Registers

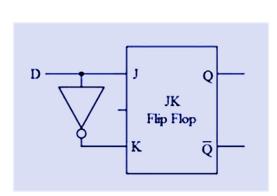

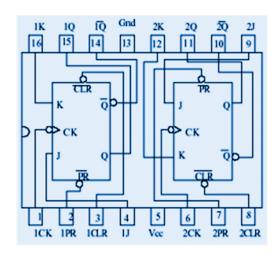

In this experiment, D Flip flops are achieved using JK Flip Flop. Connect PR and CLR to logic 1 during the experiment.

## Circuit to make D flipflop using JK flipflop:

7476 IC pin diagram (JK Flipflop).

## Inverter gate (NOT): IC 7404LS

## 2-input AND/OR/EX-OR gate: IC 7408LS/7432/7486

| input gate 1 1  | _ U  | 14 +2 to +6V HC<br>+5V LS/HCT | input gate 1 1  | - U  | 14 +2 to +6V HC<br>+5V LS/HCT |

|-----------------|------|-------------------------------|-----------------|------|-------------------------------|

| output gate 1 2 |      | 13 input gate 6               | input gate 1 2  | 7400 | 13 input gate 4               |

| input gate 2 3  |      | 12 output gate 6              | output gate 1 3 | 7408 | 12 input gate 4               |

| output gate 2 4 | 7404 | 11 input gate 5               | input gate 2 4  | 7400 | 11 output gate 4              |

| input gate 3 5  |      | 10 output gate 5              | input gate 2 5  | 7432 | 10 input gate 3               |

| output gate 3 6 |      | 9 input gate 4                | output gate 2 6 | 7486 | 9 input gate 3                |

| 0V 7            |      | 8 output gate 4               | 0V 7            | 7400 | 8 output gate 3               |

**Seriel in serial out shift register**: Construct the serial in-serial out and serial in and parallel out circuit and then demonstrate how 4 digit binary is shifted and stored in it.

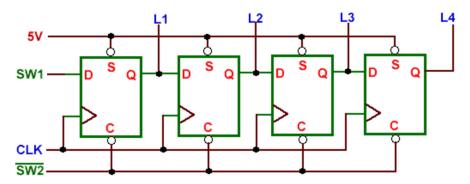

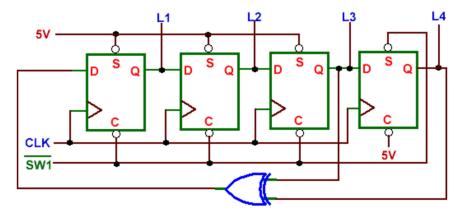

Parallel in parallel out shift register circuit diagram. SET and CLEAR are kept at logic 1 or connected to 5 V.

Observations: ....

Pseudo Random number generation (optional experiment): Different sequences of Random numbers can be generated with Shift registers and using XOR gate. Below diagram is for a good choice of XOR to generate Random number. Verify it and what are the other types Random number sequences are possible?

At each time step:

- 1. Bits 3 and 2 are combined by exclusive-or.

- 2. The register is shifted 1 step to the left.

- 3. The result of the exclusive-or is entered into bit 0.

Here is the pattern of bits, starting with 0001:

Further information on Random number generation:

http://www.cs.miami.edu/home/burt/learning/Csc609.022/random\_numbers.html